双界面智能卡芯片硬件结构及技术难点简介

引言

双界面智能卡是一种集成了接触式、非接触式两种通信界面的CPU卡。它结合了接触式和非接触IC卡的优点,接触式IC卡以它存储容量大、可靠性强、安全性高的特点,它广泛应用于金融、电信、社会保险等领域;非接触式IC卡以它无需插拔卡、操作方便、交易快速、抗环境污染和静电能力强等特点明显优于接触卡,因此,它一出现就受到人们的重视,显示出良好的应用前景,它在公共汽车、地铁、轮渡等交通一卡通领域得到广泛的应用。从2011年3月,人民银行颁布《中国人民银行关于推进金融IC卡应用工作的意见》开始,意味着我国银行磁条卡向IC卡迁移的工作全面启动,与此同时,央行选定了北京、上海、天津、济南等47个城市作为试点城市,推进金融IC卡应用,并积极支持全国各地的金融IC卡发行和推广。因为双界面卡结合了接触式和非接触IC卡的优点,所以它将会是智能卡的发展方向,也将成为我国金融IC卡的主流平台。

芯片硬件结构

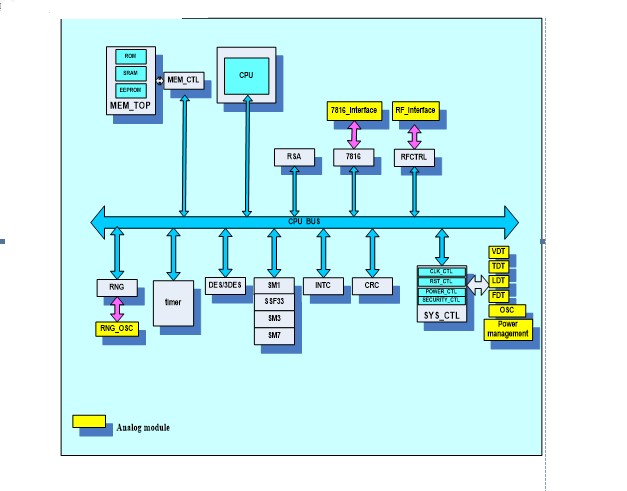

双界面智能卡芯片主要有CPU系统、界面接口、存储器、安全算法几个主要部分组成。界面接口负责和外界进行命令和数据的传输,双界面芯片提供了ISO/IEC 14443的非接触接口和基于串口通讯的接触接口,芯片共提供7个外接管脚:非接触接口的两个天线输入、接触接口的串行数据线、时钟、复位、电源和地。CPU系统主要是基于CPU的系统控制部分,包括CPU、复位控制、时钟控制等。早期的智能卡主要采用8位兼容8051指令的CPU,随着智能卡应用的多样性和应用对速度性能提出更高的要求,双界面智能卡有使用32位CPU的倾向,已有多家公司的双界面卡使用了ARM SC100 SecurCore微处理器,该处理器提供了基于高性能的32位RISC技术的一卡多用解决方案[2]。 该处理器采用三 流水结构,取指,译码,执行可形成流水操作,支持ARM和Thumb指令集及8/16/32位数据操作,具有体积小、功耗低、代码密度大和性能高等特点;支持七种操作模式和两种特权 别,同时集成存储器保护单元MPU(Memory Protection Unit), 灵活管理安全机制和安全协处理器,安全地执行存储器管理类型的功能,可以分别对存储器进行分区和设置权限,灵活实现安全域隔离和多应用;连续不分段的存储器架构,简化了软件开发。存储器部分包括存放片上操作系统(COS)的ROM和存放暂存数据的RAM及存放应用数据的EEPROM组成。为了支持多应用需求,双界面智能卡需要提供大容量的存储器,特别是为了支持JAVA,ROM需要200KB以上,RAM需要6KB以上,EEPROM需要40KB以上。算法部分主要包括DES、RSA、RNG、CRC、SM1、SM2、SM3、SM7等,部分应用需要使用国密算法如社保应用,而且我国也正在大力推动国密算法在各个行业中的应用。下面是一款上海华虹双界面智能卡SHC1302[1]的基本硬件结构:

华虹SHC1302芯片具有大容量的程序存储器、先进的EEPROM数据存储器和功能强大的多种密码加速器,集成了多个定时器、看门狗、中断控制器、真随机数发生器、CRC冗余校验、系统控制、电源管理、安全控制、射频通讯接口、接触式串行通讯接口、通用数据口等模块,不仅可应用于需要较高计算能力、高速通讯的非接触式应用系统,如电子证照、身份识别、银行金融、访问控制、签名认证、公交应用、小额支付等,还可以应用于需要较高数据传输稳定性的接触式应用系统,如社保、医保、银行金融、SIM卡、PSAM卡等。该芯片的射频通讯接口支持ISO/IEC14443协议。该芯片基于0.18 CMOS EEPROM 工艺技术,采用SC100 SecureCore处理器,拥有256K bytes程序存储器、144Kbytes高性能EEPROM以及10Kbytes RAM数据存储器。该芯片包含安全协处理器,提供丰富的硬件函数支持安全密码运算如DES、3DES、RSA和ECC(椭圆曲线加密)算法等,可以快速进行加解密、数字签名和MAC(消息验证码)运算,能够很好地满足安全访问和认证等应用的性能要求。

双界面智能卡主要技术难点

1:32位安全微处理器

SHC1302芯片中的CPU处理器是国内 在非接触及双界面智能卡产品上采用的32位安全专用微处理器,32位CPU(ARMSC100)在智能卡中的应用,实现适合智能卡应用的32位CPU体系,既能体现32位CPU的运算能力,又满足智能卡对面积和功耗的要求,并具有以下优点:

l 高运算性能

由于快速通关、密码运算、大数据量传输等应用需求,微处理器必须提供足够的运算速度才能满足应用需求。

l 高安全性

微处理器在应用过程中将承担部分敏感的密码运算处理,因此,许多攻击(如SPA、 等)都针对微处理器运行时的弱点来进行,所以,微处理器本身需要具有抗攻击的措施。此外,对于整个芯片体系来说,微处理器是一个安全体系架构建立的基础,其架构必须适合芯片软硬件系统建立一个安全的运行环境。

l 低功耗

低功耗是非接触应用的一个通用需求,对于微处理器来说也是如此。但高运算性能往往和低功耗是矛盾的需求,一味地强调速度将使得整个系统无法满足非接触的应用环境,而一味地强调低功耗则可能导致运算性能低下从而无法满足应用需求。因此,如何提高性能/功耗的比值成为技术方案中的关键。

2: 847Kbps的非接通信速率

l 能够完全支持ISO/IEC14443协议中规定的所有技术选项

l 读写机具和芯片之间的通讯上下行均能够达到847Kbps这一协议规定的 值

l 支持长数据帧的稳定通讯,根据当前协议规定,一帧 多可包含256字节的数据

l 高度可靠的编解码能力和通讯容错能力,尤其是在高速率通讯长数据帧的场合

l 需全面支持抗冲突协议

l 由于应用环境将涉及世界上各个国家,所以面临的读写机具形式多样,这对芯片的兼容性设计提出了极高的要求

l 和传统的非接触逻辑加密卡以及小容量低端的非接触式CPU卡相比,本芯片对射频通讯中的低功耗技术的依赖更为显著

3:双界面工作状态

同时实现接触式通讯接口(符合ISO 7816)和非接触式通讯接口(符合ISO 14443,并实现高速率的非接通讯接口。双界面卡集合了接触式卡与非接触式卡的优点,这使它可有多种功能,是一种多功能卡。需要解决以下技术难点:

l 双界面卡的电源管理

l 双界面卡的复位管理

l 双界面卡的时钟管理

l 双界面卡的通讯接口切换和优先 选择

4:大容量的嵌入式非挥发性存贮器技术

嵌入式非挥发性存贮器的设计要求的挑战,主要包括以下两个方面:

l 工艺水平的提升

由于高端双界面智能卡面临高速、低功耗、低成本的技术挑战,因此,采用先进的深亚微米工艺技术是至关重要的。从当前国外同类产品的工艺水平来看,普遍达到了0.13微米或0.09微米工艺水平。而相对来说,国内目前大规模的嵌入式非挥发性存贮器的应用还集中在0.18微米以上的工艺水平,距离国际上的先进水平存在一定的差距。

l 大容量低功耗的设计

根据国内的非接触式智能卡应用水平来看,目前主要还集中在8K字节以下的小容量应用上。32位智能卡芯片平台提出的64K字节以上的大容量应用需求,使得低功耗技术变得极为关键。在大容量嵌入式非挥发性存贮器设计中,华虹公司采用多项低功耗技术,有效地降低了嵌入式存贮器的功耗。

SHC1302芯片所涉及的大容量低功耗EEPROM设计有:存储体阵列分割技术、低功耗CP_HV模块设计、低功耗读出电路(senseamplify)设计等关键技术。

5:硬件加密协处理器技术

SHC1302智能卡芯片中同时实现对称加密算法硬件协处理器和公开密钥体系(PKI)硬件协处理器,因为需对数据进行全程加密,将大量地运用对称加密算法来进行,在一次交易过程中可能涉及上万次的加密运算。所以,对称加密算法的效率很大程度地影响交易速度。如何提高对称算法在应用中的效率是一个重要的问题。

公开密钥体系相对于对称加密算法往往具有运算复杂、运算速度慢、电路规模庞大的劣势,但其功能又是对称算法所无法 的。在非接触式应用中的公开密钥体系在实现过程中更是要考虑性能和功耗的平衡。

SHC1302智能卡芯片对于安全算法在硬件实现中的抗攻击提出了很高的需求,所以,在算法硬件设计时不仅仅需要考虑功能、速度、功耗、面积等这些传统的因素,实现抗攻击的措施有:

l 对称加密硬件协处理器,重点解决两个问题,一是提高整个系统的加密效率,二是实现低成本高效率的抗攻击措施。

l 公开密钥体系(PKI)硬件协处理器,实现PKI应用中的大数的加减乘除运算以及模加、模减、模乘、模幂等运算,其运算量远远超过对称加密算法运算量数个 别。该硬件协处理器必须具有以下的特点:

具有完善的功能。能够充分支持RSA的各类应用场景,如密钥对的生成、加解密、签名/签名验证等。同时为了充分考虑产品的竞争力,需要同时支持ECC算法的各类应用,并具有国密ECC算法的扩展功能。

在面积、速度、功耗之间进行合理地选择,尤其是解决速度和功耗之间的矛盾。

具有抗攻击措施。通过硬件抗攻击架构的研究,在协处理器 别即实现抗攻击功能。

6:安全攻击技术

通过以下一系列抗攻击技术在芯片中的实现,满足双界面智能卡芯片的高安全应用需求:

l 真随机数发生器技术

l 芯片抗攻击技术

l 完善的环境检测电路

l 采用安全的时钟处理技术

l 芯片物理顶层采用屏蔽层来防止检测针对芯片在工作状态时实施的探测攻击

l 芯片 抵御SPA、 攻击措施

l 基于微处理器存贮器保护单元(MPU)的硬件域隔离设计

l 物理存贮器总线的实时加解密功能

l 测试模式与应用模式的隔离,防止测试模式被功能误用

l 特殊的存贮器工艺,防止逆向解剖

l 版图的打散混乱布局

总结

本文以上海华虹高端双界面智能卡芯片SHC1302为例,介绍了双界面智能卡芯片的硬件结构以及几个设计技术难点。该芯片采用ARM公司的Secure Core(SC100), 内置ROM、RAM作为程序和数据的存储、并采用EEPROM作为数据或程序的断电存储。另外该芯片同时具有接触式和非接触式通讯接口,并集成了定时器和看门狗、时钟控制、随机数模块、中断控制器、系统控制以其高效的处理能力、强大的密码协处理能力、丰富的系统资源、多样的安全措施和多种高速通讯接口, 能够满足非接触式应用和接触式应用系统的要求,可以应用于电子护照、身份识别、社保、医保、公交、城市一卡通、电信、银行金融、移动支付等领域。

参考资料

[1] SHC1302 DataSheet

[2] http://www.arm.com

作者:舒海军